3��FPGA��·���

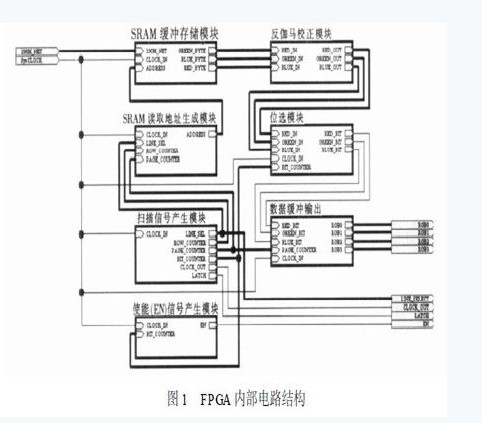

��Ƶͼ���ź�Ƶ�ʸߡ���������Ҫ��ʵʱ��������֮ȫ�ʴ���ĻLED������ʵ�ֵ��������൱���ӣ�����CPLD/FPGA��ƿ��Ƶ�·�����Լ�ϵͳ�ṹ�����ڵ��ԡ�������Ƶ�ɨ�������Ӧ���ڴ���Ļȫ��LED�ѻ���Ƶ����ϵͳ�С������漰����Ƶ�źŵĴ洢�Ͷ�ȡ����Ƶ���ݵĴ���ͽ��ա��Ҷ���ʾ���Ƶ�·��LED������ʾ������·�ȡ�������Ҫ�ԻҶ���ʾ���Ƶ�·�������ۣ����ƶ���Ϊ�Ժ졢�̡�����ɫLED��ɵ�ȫ�ʾ�̬��ʾ����ʵ�ֻҶ���ʾ��������FPGA�ڲ���·�ṹ��ͼ1��ʾ��

��LED��ʾ��ɨ����Ƶ�·�У�FPGA����������Ҫ����������������Ҫʵ����Ƶ���ݽ��ա������ԻҶ�У����ɨ���źŲ������ܡ�FP2GA�ڲ�������·ģ���Э���������������������ʾ�������������ʵ��LED��ʾ����ȫ����Ƶ���š�

��Ϊһ����������ʾϵͳ����ͨ��RS232��RS485���߷�ʽ�Ѳ�������LED��ʾ�����ж�ý����Ƶ������Ҫ�ﵽ�ĸ��������ʴ���Ҫ����512×256��ȫ����ʾ��Ϊ������Ҫ��ϵͳ��֡Ƶ�ʴﵽ30Hzʱ����Ҫ�����ݴ������ʸߴ�94.4Mbps����ˣ���ϵͳ����У���Ƶ���ݵĴ���ͽ��ղ���RTL8201��Ƶ�100M��̫������������ɡ�

Ϊ��ʹ��Ƶ��������ƽ���������ݽ��չ����в��ܴ����ʾ�������������SRAM����“ƹ�Ҳ���”��ʹ��ʾ���ݵĽ��մ洢�Ͷ�ȡ�ܹ�ͬʱ���У��Ӷ�ʵ����Ƶ���������컺��ʹ�������ͼ2��ʾ����֡�ź�FRAME_SWITCH�������л�����SRAM��ģ����źž�������SRAM��һ�鴦�ڶ�״̬����һ�鴦��д��״̬��RTL8201���ݽ���ģ�齨��MII�ӿڣ�ʵ����RTL8201�Ľӿڣ���MII�ӿڴ������İ��ֽ�����ת����Ϊ24λRGB���ݣ�Ȼ��洢��SRAM�RTL8201ÿ������һ֡��ʾ���ݣ���Ի�֡�ź�FRAME_SWITCH������������SRAM�Ķ�дλ���л�������ʹ��ʾ����ʾ���½��յ���֡���ݣ��Ӷ�ʵ�ֻ�֡������

����LED��ʾ������4�����������ʾģ�飬���ɨ����Ƶ�·��Ҫ�ṩ4·RGB��������ӿڣ���ͼ1�б�ʾΪRGB0��RGB3��

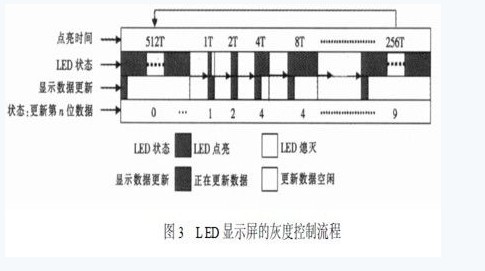

CLOCK_OUTΪ��λʱ���ź�����˿ڣ�RGB0��RGB3�ڸ�ʱ�ӵ���������Ч�������˿ڵĺ졢�̡�����ɫ��ʾ����ͨ��ʱ�������źŷֱ���λ��������оƬ����ʾ���档LATCH�ź�Ϊ�������������������Ҫ������ʾˢ��ʱ���������塣ENΪ�Ҷȿ����źţ���EN��Чʱ��LED�������������ݵ�0��1״̬Ϩ����ߵ���������Чʱ����ȶ�ӦΪ��2��ʾ�ĵ���ʱ�䡣

EN�źŲ���ģ��Ϊʵ�ֻҶ�ͼ����ʾ����Ҫģ�飬��ģ�齫�����λ����ֵת����Ϊ��Ӧλ�ĵ���ʱ�䣬��������Ӧʱ�䳤�ȵ����ȿ��ơ�

�ڱ�����У�����ĻҶ��ź�Ϊ256�������ǵ���γ������У����������ĻҶ���ʧ��������ĻҶȼ�����Ϊ1024���������Ҫ�õ�10λ�Ҷ����ݸ���λ��Ӧ�ĵ���ʱ�䡣����“�Ҷ�ʵ��ԭ��”��10λ�Ҷ����ݸ�������λ��Ӧ�ĵ���ʱ���D0��D9�ֱ��1T����Ϊ512T��������ʱ��Ϊ1023T��

����������������оƬ�ж������湦�ܣ����Ը������ݺ͵���LED���������ƹ��̿��Բ����ص����Ӷ��õ�ͼ3��ʾ��LED��ʾ���Ҷȿ������̡����µ�0λ����ʱ����ʱ��Ϊ512T�����µ�1λ����ʱ����ʱ��Ϊ1T...�������ƣ����µ�nλ����ʱ�����Ƶ�����ʱ��Ϊ��һ�������µ�λ����Ҫ�ĵ���ʱ�䡣

������һ�ִ���Ļȫ��LED��ʾ����Ƶ�ɨ��������Ʒ�����ͨ����“19��ɨ��”ʵ�ַ����ķ���������䲻��֮���������һ����ʽ����λ�����Ҷȿ��Ʒ������ÿ��Ʒ���ʹ����ȫ��LED��ʾ��������У�������LED�ķ���Ч�ʺ�ˢ����֮��������ĵ���������Ʋ���FP2GA����оƬΪ���ƽ̨�����ɨ����Ƶ�·��ʵ�֣�����EDA�������ߣ�������������·������Ѷȣ���������Ŀ�Ŀ������ڡ�

���༭��daisy��

- ���ĵ���

-

- ��3ҳ��FPGA��·���

- 12-09������ͨled��ʾ���ɰ���Ѥ���羰��

- 12-09���ݴ���LED��ʾ�� ���������ɺϷ�

- 12-09������LED��ʾ��ͨ�ü����淶����¯

- 12-09��άP6����led��ǰά�����徫��չʾ

- 12-06δ��������չLED��ʾ����ҵ���������

- 12-06���鴴�³н�������P16����led����Ŀ

- 12-06LED��ʾ����Ϯ�ɷ� ֪ʶ��Ȩ�����

- 12-05C-MARK�����仧�����������������Ƶ�

- 12-05������¯������LED��ʾ���ط���

- 12-04dz��LED��ʾ����OLED��ʾ����Ʒ������

- �������500ǿΪ������SHARP/NECȫ��LED�㾧��?

- һͼ���������Ƽ�2024�����ȱ���

- XR����������ҵPixotope���������ս�Ժ���

- ���ǵ�ѧϰ��չ���� | ��ѵʦ���顰��������

- �������2024���Ļ�鹲Ӯ�������Ϯ��

- ����The Wall����������ʾ���۽����������³���

- �ü����ƾ���ӰԺ���� �������ǵ�����BIRTV2024

- �ذ�δ�� | ���ǵ¿�������Ӫ�ɹ��ٰ�

- ���Ƴ��� �������磬COB��Ʒ��һ������࣡

- �����ռ���㼼�����ܡ�����:��ա�

- �� ��

- ���Ų�Ʒ

-

![[����]HI-P1.5](/pic/product/201308/20130809/2013080914141346.jpg)

[����]HI-P1.5

�۸�����

[�鿴����] - �۸�����[����]HI-P1.8

- �۸�����[����]HI-P2

- �۸�����[����]HI-P2.5

- �۸�����[����]HI-P3

- �۸�����[����]HL-VW P3.0

- �۸�����[����]HL-VW P2.5

- �۸�����[����]P10��ש��

- �۸�����[����]P18.75��Ļ

- �۸�����[����]P10.41��Ļ

�������� | ��ϵ���� | �������� | ��ƸӢ�� | ������� | ��Ȩ���� | ��վ��ͼ | ������ | ��ӭͶ�� | ���ע��

��Ȩ���� ���������� Copyright © 2006-2019. All Rights Reserved ��ICP��06048189��-2 �����й����ֳ����־��������ı�����ţ�1101051445

QQȺ��������Ⱥ(146100746) ������Ⱥ(160287492) ͶӰ��Ⱥ(154576638) רҵ����Ⱥ(160287677)

�������ߣ�010-62536866/82627795 ���棺010-82627795

![[����]LED ��Ϣ��ʾ��](/pic/product/200907/20090707/2009070710344194.jpg)

![[��̩]���ڦ�3.0˫��ɫ](/pic/product/200904/20090402/2009040213544474.jpg)

![[��ʢ]P10���ⵥɫLED��](/pic/product/200904/20090403/2009040311333292.jpg)

![[�����ι�]KR-3906/2R1G](/pic/product/200906/20090615/2009061513594562.jpg)

![[Ӧ�캣��]����LED��](/pic/product/200912/20091214/2009121414224919.jpg)

![[����]P10.41��Ļ](/pic/product/201209/20120912/2012091211425721.jpg)